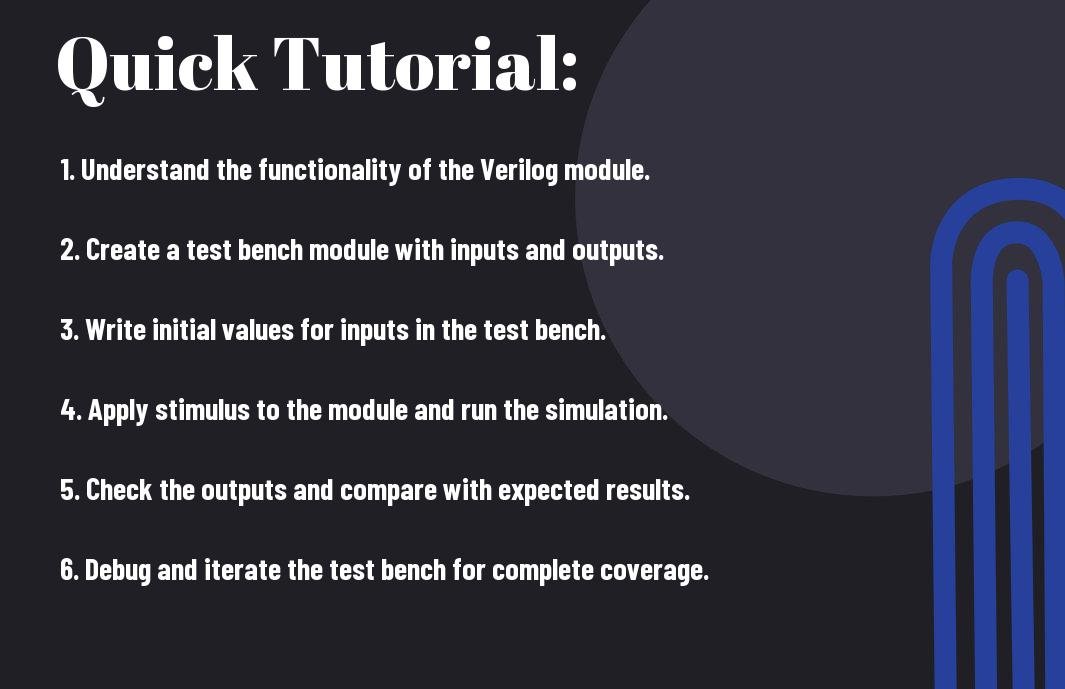

Perplexed about creating a robust test bench in Verilog? In this tutorial, I will reveal essential techniques that experts often keep to themselves. Building an effective test bench is crucial for verifying the functionality of your Verilog code and finding bugs before they become costly errors in your final design. By the end of this post, you will have a clear understanding of the steps to take and the dangerous pitfalls to avoid when creating a test bench in Verilog. So, roll up your sleeves and let’s dive into the powerful techniques that will take your Verilog skills to the next level.

Key Takeaways:

- Understanding test bench in Verilog: Learn the basic concepts and importance of test bench in Verilog for effective testing of your designs.

- Proper code structuring: Explore the techniques and best practices for organizing your Verilog test bench code to improve readability and maintainability.

- Advanced simulation techniques: Discover expert-level strategies for efficient and thorough simulation of your Verilog designs using advanced test bench techniques.

- Effective debugging methods: Gain insights into the tools and methods for efficient debugging of Verilog test benches to identify and address issues in your designs.

- Maximizing test coverage: Learn the expert tips and tricks for maximizing the test coverage of your Verilog designs through well-crafted test benches.

Basics of Test Benches in Verilog

A test bench is a crucial component in the process of verifying the functionality of a design in Verilog. It is a module that instantiates the design under test (DUT) and applies stimulus to it, as well as checking the responses from the DUT. In this chapter, I will cover the basics of test benches in Verilog, including what they are, why they are important, and common techniques for writing them.

What is a Test Bench

A test bench is essentially a simulation environment for your Verilog design. It consists of a module that instantiates the DUT and provides the necessary stimulus to verify its functionality. This includes applying input signals and monitoring the output signals to ensure that the DUT is behaving as expected. In essence, the test bench serves as a virtual environment in which the DUT can be thoroughly tested before it is implemented in hardware.

Importance of Writing a Test Bench

Writing a test bench is a critical aspect of the design process in Verilog. It allows you to verify the correctness of your design, identify potential bugs or errors, and ensure that the design meets the specifications and requirements. Without a robust test bench, it is virtually impossible to fully validate the functionality and performance of your design. In essence, your test bench acts as a safety net, catching any potential issues before they manifest in the physical implementation.

Common Techniques for Writing Test Benches

There are several common techniques for writing test benches in Verilog, each with its own pros and cons. These techniques include manual test bench writing, using Verilog tasks and functions, and using specialized simulation tools such as SystemVerilog or Verilog-AMS. Each technique has its own strengths and weaknesses, and choosing the right one depends on the specific requirements and constraints of your project. It is crucial to select the most appropriate technique for your specific design and verification needs to ensure the effectiveness and efficiency of your test bench.

Advanced Techniques for Writing Test Benches

If you’re looking to take your test bench writing skills to the next level, there are several advanced techniques that you can implement to ensure thorough testing and efficient verification. Here are some key strategies to consider:

- Using Functional Coverage and Assertions

- Implementing Constrained Random Testing

- Using SystemVerilog for Advanced Test Bench Writing

Using Functional Coverage and Assertions

When it comes to verifying the functionality of your design, leveraging functional coverage and assertions is crucial. Functional coverage ensures that all essential functionality of the design has been exercised during simulation, while assertions help to maintain design integrity by checking for specific conditions or properties. By utilizing these techniques, you can gain greater confidence in the correctness of your design and identify any potential issues early in the verification process.

Implementing Constrained Random Testing

Constrained random testing is a powerful technique that allows you to thoroughly exercise the functionality of your design by generating a diverse set of test cases based on specified constraints. This approach enables you to efficiently explore the design space and uncover corner-case scenarios that may not be addressed through traditional directed testing methods. By implementing constrained random testing, you can uncover potential bugs and ensure comprehensive verification of your design.

Using SystemVerilog for Advanced Test Bench Writing

SystemVerilog provides a rich set of features that can significantly enhance your test bench writing capabilities. From the conciseness of the language to the built-in support for object-oriented programming, SystemVerilog offers a wide range of tools and methodologies for creating efficient and reusable test benches. By leveraging the advanced capabilities of SystemVerilog, you can streamline your verification process, increase productivity, and uncover subtle bugs that may go undetected with traditional Verilog test benches.

Tips and Best Practices for Writing Test Benches

For writing efficient and effective test benches, I have compiled a list of tips and best practices that will help you in your Verilog programming journey. These tips will assist you in writing robust test benches that accurately simulate and verify your design.

- Use meaningful stimulus: When writing your test bench, make sure to use meaningful input stimuli that thoroughly exercises your design. This will help you catch any unintended bugs or design flaws.

- Modularize your test bench: Break down your test bench into smaller, manageable modules to improve readability and maintainability of your code. This will also make it easier to reuse specific parts of your test bench in future projects.

- Utilize assertions: Incorporating assertions in your test bench can be extremely helpful in verifying the correctness of your design. They can be used to check for specific conditions or properties within your design.

- Randomize inputs: Introducing randomization in your test bench can help uncover corner cases and potential issues in your design. This will enhance the thoroughness of your verification process.

This approach to writing test benches will ultimately save you time and effort in debugging and troubleshooting issues in your design. By incorporating these practices, you can ensure that your test bench effectively validates the functionality of your Verilog code.

Debugging and Troubleshooting Test Benches

When it comes to debugging and troubleshooting test benches, one of the most effective techniques is to use print statements strategically. Printing out specific signal values or checkpoints in your test bench can help you pinpoint where the issue lies. Additionally, running simulations in smaller increments can make it easier to identify the root cause of any problems. Understanding the functionality of the tools at your disposal, such as simulators and waveform viewers, is essential for efficient debugging. This knowledge will enable you to efficiently track down and resolve any issues in your test bench.

Writing Reusable Test Benches

When aiming to write reusable test benches, it is important to focus on creating generic and configurable modules. This will allow you to easily adapt your test bench to different design scenarios without having to start from scratch each time. Thorough documentation of your test bench’s functionality and usage is crucial for promoting reusability. By clearly outlining how to use and modify your test bench, you can ensure that it is easily understandable and adaptable for future projects.

Optimizing Test Bench Performance

When it comes to optimizing test bench performance, minimizing unnecessary delays and redundant operations is key. Strive to keep your test bench code as efficient as possible, as this will ultimately speed up simulation times and improve overall productivity. Implementing parallel testing and using advanced verification methodologies such as UVM (Universal Verification Methodology) can also significantly enhance test bench performance. By leveraging these techniques, you can ensure that your test bench operates at its optimal level, allowing for swift and thorough verification of your Verilog designs.

Summing up the Verilog Test Bench Techniques

In conclusion, writing test benches in Verilog is an essential skill for any digital design engineer. Through various techniques and best practices, you can effectively create thorough and efficient test benches that uncover potential design flaws and ensure the functionality and performance of your design. As an expert in Verilog test bench development, I have shared key insights and strategies that will streamline your verification process and lead to more reliable and robust digital designs. By incorporating these techniques into your own practice, you can elevate your verification process and produce high-quality digital designs.

FAQ

Q: What is a test bench in Verilog?

A: A test bench in Verilog is a module that is used to apply stimulus to a design under test (DUT) and observe its behavior. It is crucial for verifying the correctness of the DUT and ensuring that it meets the design specifications.

Q: Why is writing a test bench important in Verilog?

A: Writing a test bench is important in Verilog because it allows for thorough testing and debugging of the DUT. It helps in identifying and fixing any issues in the design before it is implemented, thus ensuring the overall reliability and functionality of the final product.

Q: What are the techniques for writing an effective test bench in Verilog?

A: Some techniques for writing an effective test bench in Verilog include using good coding practices, creating comprehensive test cases, incorporating functional coverage, and utilizing assertion-based verification. These techniques help in achieving better test coverage and improved verification results.

Q: How can I create realistic stimulus for the DUT in a Verilog test bench?

A: To create realistic stimulus for the DUT in a Verilog test bench, you can use randomization, constrained random testing, and intelligent stimulus generation techniques. This will help in simulating real-world scenarios and edge cases, thus providing more thorough testing of the design.

Q: What are some advanced tips for writing a test bench in Verilog that experts use?

A: Some advanced tips for writing a test bench in Verilog that experts use include incorporating functional coverage-driven testing, using assertions for formal verification, and leveraging advanced debugging and simulation tools. These tips can enhance the efficiency and effectiveness of the verification process.